# シリコン基板上 GaN の高分解 TEM 観察 HR-TEM Analyses of GaN grown on silicon substrate

澤木宣彦<sup>†</sup>,岩田博之<sup>†</sup>, 川北将吾<sup>†</sup>,本田善央<sup>† †</sup> Nobuhiko Sawaki<sup>†</sup>, Hiroyuki Iwata<sup>†</sup>, Shogo Kawakita<sup>†</sup>, and Yoshio Honda<sup>† †</sup>

**Abstract** Growth of a high quality GaN on a silicon substrate has been attempted. In order to prevent Ga-Si reaction at high temperatures, an AlInN alloy was tested as the intermediate layer between the GaN grown layer and the Si substrate. It was found that growth of thin AlN layer followed by the growth of AlInN intermediate layer could improve crystalline quality of the GaN top layer. The density of threading dislocation as well as point defect are reduced substantially. High resolution (HR-) TEM analyses showed that the AlN layer has been grown on Si substrate introducing misfit dislocation. Moreover, the AlInN layer has also been grown epitaxially introducing misfit dislocations as predicted by nominal lattice constants at room temperature.

#### 1. 緒言

革新的な創・省エネルギー技術開発への世界的な期待は、地球規模での人口の爆発的増加と発展途上国といわれた国々での電子機器の普及によるエネルギー消費量の劇的な増加への対応を迫られたことによるものであった。我が国では、総人口増加は見られないものの少子高齢化が進む中で上記の世界的動向を受けて、最も得意とする分野として投資が続けられてきた。平成23年3月11日に起こった東日本大震災と福島第1原子力発電所事故に伴う発電能力の低下が引き金となり、さらに世界的な金融(経済)危機が相乗して、創エネルギー・省エネルギー技術開発が待ったなしの状況に追い込まれるに至った。

20世紀後半に開発され、現代の生産技術を牽引する半導体技術は、過去50年余に亘って、情報・制御技術の革新をもたらし、我々の生活様式(文化)の変革を促した。この間の技術革新によって各種機器・システムの高効率化・省エネルギー化が進められたにもかかわらず、利用される機器総数の増加がそれを上回り、結果として総エネルギー消費量は増加の一途をたどることとなった。21世紀に求められる技術は、まさに革新的(抜本的)な創・省エネルギー技術である。

現代の工場の生産ラインや日常生活に使われる情報処

理機器にはシリコン集積回路が使われ、航空機・電車・自動車などの制御もシリコン制御素子が使われている。処理すべき情報量(質)の増加に対応するため、微細加工技術の高度化と光素子との融合技術が検討され、他方では、電力素子における省エネルギーのためさらなる低電力損失素子の開発が望まれている。また、各所で設置が進められている Si 太陽電池の効率は 20%程度にとどまり、さらなる高効率化が望まれている。

本研究は、広いエネルギーバンドギャップを有するⅢ族 窒化物半導体材料に関する。窒化物半導体は青色 LED 材 料として開発され、緑色、赤色と共に三原色 LED の構成 を可能とし、フラットパネルフルカラーディスプレイや交 通信号機の高度化、白色 LED の開発に大きく貢献した。 福島第1原発事故以来、我が国政府は、省エネルギーのた め白色 LED 電球の普及を推奨している。しかし、白色 LED はサファイア基板上に作製されるため、作製コストが高止 まりしている上に演色性に難(暖色発現が困難)がある。 また、電気自動車等(EV、HV)では燃費のさらなる改善の ため、電力損失の少ない電力制御素子の開発が望まれてい る。本研究では、シリコン基板上への高品質 GaN の作製 技術を確立することによって、白色 LED、インバータ用ト ランジスタ、高効率太陽電池の高度化に貢献することをめ ざしている[1]。そのために必要不可欠の、シリコン基板上 での高品質 GaN の作製のための緩衝層技術の確立、高濃 度 p 形伝導 AlGaN の作製技術の確立を目的として、 MOVPE 結晶を高分解 TEM 像観察等により評価した。

<sup>†</sup> 愛知工業大学 工学部電気学科(豊田市)

<sup>† †</sup> 名古屋大学 工学研究科電子工学専攻(名古屋市)

### 2. 実験方法

### 2.1 GaN/AlInN/Si の MOVPE 成長

立方晶シリコン基板上にウルツ鉱構造の GaN を直接エピタキシャル成長することは出来ない。その上、GaN と Si とは高温でよく反応し GaSiN 混合物を生成するため、1000℃程度の成長温度で安定的に GaN をエピタキシャル成長させるためには緩衝層の挿入が必要である。本研究では、Ga元素を含まない AlInN 混晶を緩衝層として用い、その効果を検証することを内容としている。エピタキシャル成長は名古屋大学大学院工学研究科クリーンルームで行った[2]。

本研究で用いた試料の概要を表1に示す。成長温度で Si 基板表面は容易に酸化あるいは窒化するため、成長前に、最表面には Al を吹きつけ、更に窒素ガスを供給することにより薄い AIN 膜を形成した。その上に AlInN 緩衝膜を形成し、GaN を成長させた。

表 1 GaN/AlInN/AlN/Si 試料の緩衝層膜厚

|     | AlInN 成長時間 | AlInN 膜厚 | 基板      |

|-----|------------|----------|---------|

| # 1 | 5min       | 16nm     | (111)Si |

| # 2 | 10         | 33       | (111)Si |

| #3  | 20         | 65       | (111)Si |

|     |            |          |         |

### 2.2 TEM·PL 評価

本実験では、AlInN 緩衝層の効果を検証するため、AlInN 成長時間すなわち AlInN 膜厚を変化させ、上部 GaN 層に誘起する貫通転位密度の変化を評価した。TEM 観察には愛知工業大学総合技術研究所に設置されている透過電子顕微鏡 JEM-2010 を、PL 評価には同研究所に設置されている顕微紫外可視近赤外分光光度計 (NRS-5100PL)を用いた。

### 3. 実験結果

## 3.1 貫通転位密度の評価

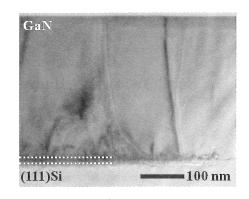

図1に試料#1の典型的な断面 TEM 像を示す。下地の Si 基板上に薄い AlInN 緩衝層を介して 400nm 程度の GaN 層 が成長されていることが見て取れる。ここで、黒い陰影部 分が欠陥を示している。ヘテロ界面近傍の 50nm 程度までの範囲には暗い部分が集中し高密度の結晶欠陥が含まれていることが分かる。他方で、結晶の上部では暗い部分は無く、欠陥の少ない結晶が得られていることが分かる。

GaN/AlInN 層内で Si 基板との界面から縦方向に線状に伸びている暗い部分は貫通転位の存在を示している。この試

料には観察している範囲内に 1 本の貫通転位があることになる。この断面 TEM 像で見られる貫通転位の本数から貫通転位密度(試料表面で単位面積あたり観察される貫通転位の密度)を推定できる。

図1 GaN/AlInN/AlN/Siの断面 TEM 像

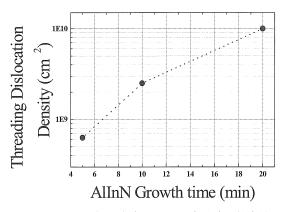

図2 貫通転位密度の AlInN 成長時間依存性

貫通転位の密度や種類は試料の作製条件によって変化することが知られている。表1に示した3種類の試料について断面 TEM 像を解析して貫通転位密度を評価した結果を図2に示している。1 cm $^2$  あたり10E8 台から10E10 台まで大きく変化することが分かる。本実験の範囲では、AlInN層厚が薄いほど貫通転位密度の低い試料が得られるといえる。

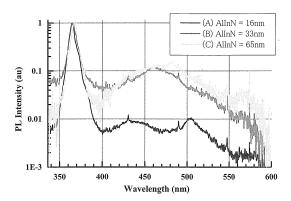

結晶品質を他の指標から評価するため、室温におけるホトルミネッセンス(PL)スペクトルを測定した。励起は He-Cd レーザの 325.29nm の発振線を用い、顕微鏡を介してエミッションスペクトルを評価した。検知器は CCD である。スペクトルにはいずれの試料も 365nm に強いバンド端発光が見られ、青色領域と黄色領域に弱いブロードな発光帯が見られた。後者は格子欠陥(点欠陥)に基づくものとされている典型的な発光帯と一致している。図 3 に各試料のバンド端発光強度で規格化したスペクトルを示した。AIInN の膜厚が最も薄い試料で、点欠陥による発光帯の強度が弱いことが分かる。この結果は TEM 観察結果 (貫通転位密度の傾向)と一致し、薄い AIInN 緩衝層で高品質 GaN 層が得られるこ

とを示している。

図3 GaN/Si の室温 PL スペクトル

AlInNとその上に成長させる GaN との格子定数差は In 組成によって変化し、In 組成が 0.2 程度で最小になることが分かっている。本実験で得られた In 組成は 0.06~0.07 と低いため、格子定数差が大きく貫通転位密度の低減が困難であると予想されるにもかかわらず、薄い層とすることで単位面積あたり 10E8 台の低密度が達成されたことは注目に値する。さらに In 組成を高くすることでさらなる低減が達成できる可能性がある。

### 3.2 格子像による格子整合評価

Si(111)表面の結晶構造は3回対称性を有するのに対して、ウルツ鉱構造 GaN の(0001)面は6回対称性を有するため、格子定数の整合性さえ整えばエピタキシャル成長が可能である。しかるに、格子定数は19%もの違いがあるため、緩衝層の挿入が必要である。さらに、GaNとSiとは1000℃程度の高温では強い反応性があり GaSiN 混合物を生成するため、ヘテロ界面の安定性に問題が残る。そのため、Si基板上への GaN エピタキシャル成長には AIN あるいは AIGaN 緩衝層が用いられる。AINとSiにも大きな格子定数差があるため、いずれにせよ緩衝層の最適化が高品質 GaN 成長の鍵となる。本研究では、Ga元素を含まない AIInN の緩衝層としての適性を評価している。

緩衝層の役割は基板 Si の格子と成長層である GaN の格子との接続である。従って、格子整合は下地の Si に対する整合に加えて、成長層の GaN に対する整合条件を確立する必要がある。従来、GaN/AIN 超格子構造など薄膜の積層構造が試みられてきたが、その手法は、格子定数差がある場合でも特定の膜厚(臨界膜厚)までは成長層が下地の格子定数に引っ張られ歪みを内在したままエピタキシャル成長できるという原理を用いている。この手法によりすでに 6 インチ Si 基板上にクラックフリーGaN 成長が得られている。しかし、複雑な成長プロセスを要し製造コストの低減の支

障となっている。簡単なプロセスで、良質な成長層・緩衝層を得る技術の開発が望まれているのである。

AlInN 混晶の格子定数は In 組成により変化させることが 出来る。GaN 成長層と AlInN 緩衝層との格子定数は In 組成 約 20%の時一致すると予想される。一方、Si 基板と AlInN との格子定数は In 組成によらず一致しない。そのため、 AlInN と Si とのヘテロ界面にはミスフィット転位が不可避 的に発生する。我々は Si 基板上に AlInN 緩衝層を直接堆積した後の GaN 成長を試みたが有意な結果は得られなかった。そのため、本研究では AlN 薄膜と AlInN 薄膜との複合膜を緩衝層とする GaN 成長を試み、ヘテロ界面のミスフィット転位を評価することとした。

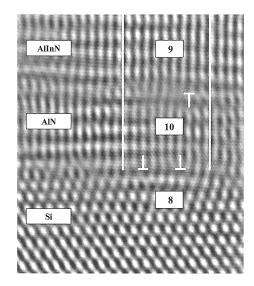

図4に試料#2の高分解(HR-)TEM像を示す。この像は図1と同様にSi(001)基板の(1-10)断面を見ていることから、図4のSi基板側での格子像はSi立方晶格子を反映していると理解される。その上で、AIN層並びにAIInN層の像を見ると、Siの<111>軸に平行(ヘテロ界面に垂直)に六方晶格子が出来ていることが分かる。格子像の明暗から格子定数差を見積もることが出来る。図中黄色の線を付した部分に着目すると、Si基板側で8個の格子に対応して、AIN層は10個、AIInN層は9個の格子が対応していることが見て取れる。相互の界面では、それぞれ2個あるいは1個のミスフィット転位(格子列の繋がらない場所)があることになる。この状況はGaAs/MnAs系で見いだされた疑似格子整合成長と類似している[3]。

図 4 AlInN/AlN/Si ヘテロ界面の格子像

ヘテロ界面方向 (a 軸) における AIN の格子定数は 0.3112nm で、Si の(111)面における等価的な格子定数は 0.384nm である。このことから、両者には Si を基準にして 18.9% (AIN を基準にして 20.4%)の格子不整合がある。図 4

の結果はこのことと一致している。さらに、InN の格子定数は AIN のそれより大きいため、AIInN 混晶とすることにより Si の実効的な格子定数に近づけることが可能となる。図4では黄色で囲った部分では AIN10 個に対して AIInN9 個が対応するものの、その左側では、明確なミスフィット転位を同定することが出来ない。すなわち、混晶としての格子定数に揺らぎ(組成揺らぎ)があることを反映していると思われる。

図4で示した試料の AIN 膜の厚さは 4~5 格子すなわち、2nm 程度と見積もられ、AIN 成長時間から予想される値と一致している。この厚さは臨界膜厚より薄いため、単結晶膜が得られているとも考えられるが、格子定数差があまりにも大きいためコヒーレント成長が出来ず、ミスフィット転位の導入により格子定数差を補っていることになる。さらにその上の AIInN 膜厚は 33nm と厚く、AIN との間の歪みの影響を無視できない。コヒーレント成長と格子緩和による成長が予想されるが、格子像はミスフィット転位を導入することにより部分的に疑似格子整合した単結晶膜が得られていることを示している。

以上の結果、薄い AIN 膜を介することで AIInN 層と Si との格子整合条件が大幅に緩和され、高品質の AIInN 従って高品質の GaN が得られることが分かる。AIInN と GaN との格子整合は In 組成を最適化することによって達成されることから、本手法では、今後薄い AIN 膜を通してさらに高品質 (揺らぎの少ない) AIInN を得る成長条件を確立することが求められる。

# 5. 結言

Si 基板上への窒化物半導体結晶成長における成長層の高品質化のため、AlInN 緩衝層の適性について検討した。薄い AlInN 膜を薄い AlN 結晶核生成層とともに形成することによってその上に MOVPE 成長した GaN 中の転位が低減されることが分かった。また、ホトルミネセンススペクトルにおける青色帯ならびに黄色帯発光も弱くなり、点欠陥密度も低減されることが分かった。

さらに、高分解 TEM 観察により、ヘテロ界面近傍の格子整合を評価したところ、Si 基板上にミスフィット転位を含みながら AIN 薄膜ならびに AIInN 膜が形成されることが分かった。今後、AIInN 中間層形成条件の最適化により成長層の一層の高品質化が期待される。

#### 謝辞

本研究は、文部科学省私立大学戦略的研究基盤形成支援経費 (平成 22 年度~26 年度:プロジェクト S1001033) ならびに日本学術振興会科学研究費補助金基盤研究(B)22360009の援助を受けて行われた。MOVPE 法による結晶成長は名古屋大学大学院工学研究科クリーンルームで行われた。試料作製にご協力頂いた同大学院生、小出典克氏(現:ILJIN社)、入江将嗣氏(現:デンソー)、日頃から議論示唆を頂く天野浩氏(名古屋大学)並びに加地徹氏(豊田中央研究所)に紙面を借りて感謝する。

### 参考文献

- [1] N.Sawaki, T.Hikosaka, N.Koide, S.Tanaka, Y.Honda, and M.Yamaguch, "Growth and properties of semi-polar GaN on a patterned silicon substrate," Journal of Crystal Growth 311 (2009) 2867–2874.

- [2] M.Irie, N.Koide, Y.Honda, M.Yamaguchi, and N.Sawaki, "MOVPE growth and properties of GaN on (111)Si using an AlInN intermediatelayer," Journal of Crystal Growth 311 (2009) 2891–2894.

- [3] K. Ploog, "Materials engineering of advanced device structures by heteroepitaxy of large misfit systems," Mat. Sci. Semicon. Process. 4(2001)451-457.